## MEMORY PERFORMANCE EVALUATION OF HIGH THROUGHPUT SERVERS

by

## GARBA YA'U ISA

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

In Partial Fulfillment of the Requirements for the Degree of

## MASTER OF SCIENCE

IN

## COMPUTER ENGINEERING

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

Dhahran, Saudi Arabia

June 2003

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA DEANSHIP OF GRADUATE STUDIES

This thesis, written by

### GARBA YA'U ISA

under the direction of his Thesis Advisor and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

Dr. Abdul Waheed M. A. Sattar (Chairman)

Prof. Sadiq M. Sait (Member)

Dr. Farrukh M. Khan (Member)

Department Chairman Prof. Sadiq M. Sait

Dean of Graduate Studies Prof. Osama A. Jannadi

Date

To My Parents and Entire Family

## Acknowledgements

First and foremost, my gratitude to my Creator and Sustainer, Allah (SWT) for all the favors He has bestowed on me throughout my life. Peace and Blessings be upon His messenger, Muhammad (PBUH), the Seal of Prophets and Messengers. Million of thanks to my parents, brothers and sisters for all the prayer and support.

My utmost gratitude to my advisor, Dr. Abdul Waheed, for his guidance, enlightenment and encouragement throughout this work. My deepest gratitude to my thesis committee member and department chairman, Dr. Sadiq Sait, for the great support in this work and throughout my stay in the department. Also, my appreciation to Dr. Muhammad Farrukh Khan, for serving in my thesis committee and for the advice and guidance he offered.

Thanks to Balarabe Yusha'u of Mathematical Sciences Department, KFUPM, for his immeasurable help while I was seeking admission to KFUPM and during my academic expedition at KFUPM. Also, my thanks to the entire Nigerian community in KFUPM for all support. Immense gratitude to my PEL (Performance Engineering Laboratory) associates: Sarif, Amisu, Faheem, Sana'ullah and Sami. Thanks to Khalid El-Badawi of Information and Computer Science, for the informative discussions on C language coding and for translating the abstract to Arabic. Many thanks to my friends back in Nigeria, especially Hamisu Shehu Umar.

Acknowledgement is due to King Fahd University of Petroleum and Minerals, for providing the resources for this research.

# Contents

|                    | Ack  | nowledgements i                 | v  |  |  |  |

|--------------------|------|---------------------------------|----|--|--|--|

|                    | List | of Tables                       | x  |  |  |  |

|                    | List | of Figures 2                    | xi |  |  |  |

| Abstract (English) |      |                                 |    |  |  |  |

|                    | Abs  | tract (Arabic) x                | v  |  |  |  |

| 1                  | Intr | oduction                        | 1  |  |  |  |

|                    | 1.1  | High Throughput Servers         | 2  |  |  |  |

|                    |      | 1.1.1 Server Performance Issues | 2  |  |  |  |

|                    |      | 1.1.2 Memory Hierarchy          | 4  |  |  |  |

|                    | 1.2  | Problem Statement               | 5  |  |  |  |

|                    | 1.3  | Contributions of this Work      | 6  |  |  |  |

|                    | 1.4  | Thesis Overview                 | 7  |  |  |  |

| <b>2</b> | Bac | kground and Related Work                                  | 9 |

|----------|-----|-----------------------------------------------------------|---|

|          | 2.1 | Introduction                                              | 9 |

|          | 2.2 | Server Performance Tuning                                 | 0 |

|          |     | 2.2.1 Memory Performance Tuning                           | 0 |

|          |     | 2.2.2 Latency Hiding and Multithreading                   | 3 |

|          |     | 2.2.3 Multiprocessing and Clustering                      | 4 |

|          |     | 2.2.4 Specialized Architectures                           | 5 |

|          | 2.3 | Examples of High Throughput Servers                       | 5 |

|          |     | 2.3.1 Web Servers                                         | 6 |

|          |     | 2.3.2 Streaming Servers                                   | 6 |

|          |     | 2.3.3 Proxy Servers                                       | 7 |

|          |     | 2.3.4 Software Routers and IP forwarding                  | 8 |

|          | 2.4 | Evaluation Methodologies                                  | 0 |

|          | 2.5 | Related Work                                              | 1 |

|          |     | 2.5.1 Improving Memory Performance                        | 1 |

|          |     | 2.5.2 Performance Evaluation of High Throughput Servers 2 | 4 |

|          |     | 2.5.3 Software Routing and IP Forwarding                  | 9 |

| 3        | Ana | lysis of Memory Accesses 3                                | 2 |

|          | 3.1 | Introduction                                              | 2 |

|          | 3.2 | Data Flow Issues                                          | 3 |

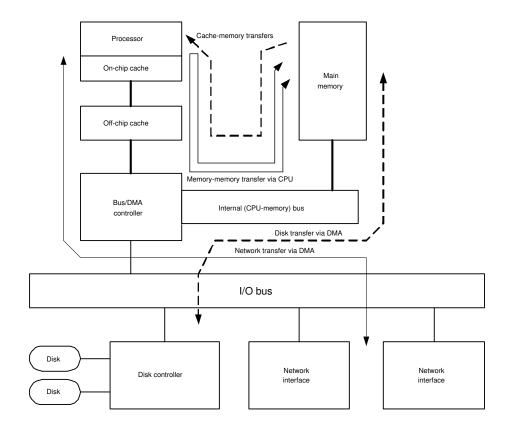

|   | 3.3  | Laten  | cy Model and Memory Overhead                          | 33 |

|---|------|--------|-------------------------------------------------------|----|

|   |      | 3.3.1  | Memory-CPU Transfers                                  | 35 |

|   |      | 3.3.2  | Memory-Memory Transfers                               | 39 |

|   |      | 3.3.3  | Memory-I/O and Memory-Network Transfers               | 40 |

|   | 3.4  | Refere | ence Applications                                     | 41 |

|   |      | 3.4.1  | RTP Transaction Latency                               | 41 |

|   |      | 3.4.2  | HTTP Transaction Latency                              | 43 |

|   |      | 3.4.3  | IP Forwarding Latency                                 | 44 |

| 4 | Мо   | Suror  | nent-Based Performance Evaluation                     | 48 |

| 4 | WIEd |        |                                                       |    |

|   | 4.1  | Introd | luction                                               | 48 |

|   | 4.2  | Exper  | imental Testbed and Tools                             | 49 |

|   | 4.3  | Analy  | sis of Operating System Role                          | 52 |

|   |      | 4.3.1  | Memory Throughput                                     | 52 |

|   |      | 4.3.2  | Multithreading Support and Context Switching Overhead | 54 |

|   | 4.4  | Stream | ning Media Servers                                    | 55 |

|   |      | 4.4.1  | Experimental Design                                   | 56 |

|   |      | 4.4.2  | Benchmarking Tools                                    | 58 |

|   |      | 4.4.3  | Performance Evaluation                                | 59 |

|   | 4.5  | Web S  | Servers                                               | 67 |

|   |      | 4.5.1  | Experimental Design                                   | 67 |

|   |                                               | 4.5.2                                                                   | Benchmarking Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70                                                                                             |

|---|-----------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   |                                               | 4.5.3                                                                   | Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70                                                                                             |

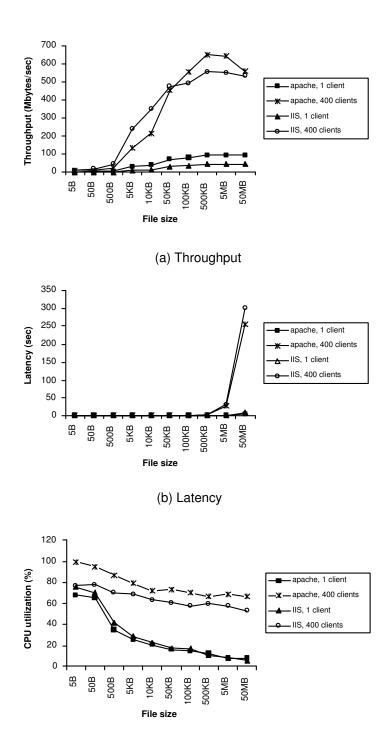

|   | 4.6                                           | Softwa                                                                  | are Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80                                                                                             |

|   |                                               | 4.6.1                                                                   | Communication Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81                                                                                             |

|   |                                               | 4.6.2                                                                   | Experimental Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82                                                                                             |

|   |                                               | 4.6.3                                                                   | Benchmarking Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83                                                                                             |

|   |                                               | 4.6.4                                                                   | Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83                                                                                             |

|   | 4.7                                           | Summ                                                                    | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90                                                                                             |

| 5 | Des                                           | ign. Ir                                                                 | nplementation, and Performance Evaluation of a Double                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                |

|   |                                               | 0 /                                                                     | P(DB-RTP) Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91                                                                                             |

|   | Dui                                           | IOI IUI                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u> </u>                                                                                       |

|   | 5.1                                           |                                                                         | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

|   |                                               | Introd                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 91                                                                                             |

|   | 5.1                                           | Introd                                                                  | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91<br>92                                                                                       |

|   | 5.1                                           | Introd<br>Desigr                                                        | uction       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <th>91<br/>92<br/>92</th> | 91<br>92<br>92                                                                                 |

|   | 5.1                                           | Introd<br>Design<br>5.2.1<br>5.2.2                                      | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>91</li> <li>92</li> <li>92</li> <li>93</li> </ol>                                     |

|   | 5.1<br>5.2                                    | Introd<br>Design<br>5.2.1<br>5.2.2<br>Impler                            | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ol> <li>91</li> <li>92</li> <li>92</li> <li>93</li> </ol>                                     |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Design<br>5.2.1<br>5.2.2<br>Impler                            | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul><li>91</li><li>92</li><li>92</li><li>93</li><li>95</li></ul>                               |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Design<br>5.2.1<br>5.2.2<br>Impler<br>Exper                   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>95</li> <li>96</li> </ul>             |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Introd<br>Design<br>5.2.1<br>5.2.2<br>Implen<br>Exper<br>5.4.1<br>5.4.2 | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>95</li> <li>96</li> <li>98</li> </ul> |

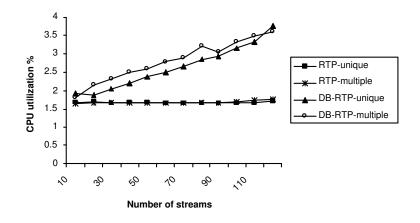

|   |     | 5.5.2   | ſ             | hro  | ough | put | an  | d ( | CPU  | JU   | tili          | zat | ior | 1. | • | • | <br>• | <br>• | • | • | • | <br>• | . 100 | )      |

|---|-----|---------|---------------|------|------|-----|-----|-----|------|------|---------------|-----|-----|----|---|---|-------|-------|---|---|---|-------|-------|--------|

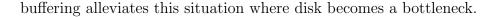

|   |     | 5.5.3   | F             | ack  | et I | oss | an  | d J | itte | er.  |               |     |     |    |   |   | <br>• |       |   |   |   |       | . 102 | 2      |

|   | 5.6 | Summ    | nar           | у    |      | ••• |     |     |      | •    | •••           |     |     |    | • |   | <br>• |       |   |   | • |       | . 103 | ;      |

|   |     |         |               |      |      |     |     |     |      |      |               |     |     |    |   |   |       |       |   |   |   |       |       |        |

| 6 | Cor | nclusio | $\mathbf{ns}$ | an   | d F  | utu | ire | Di  | rec  | ctio | $\mathbf{ns}$ |     |     |    |   |   |       |       |   |   |   |       | 105   | ;<br>) |

|   | 6.1 | Conclu  | lusi          | ons  |      |     |     |     |      | •    |               |     |     |    |   |   | <br>• |       |   |   |   |       | . 105 | ;      |

|   | 6.2 | Open    | Q             | ıest | ions |     |     |     |      | •    | • •           |     |     |    | • |   | <br>• |       |   |   |   |       | . 107 | ,      |

|   | 6.3 | Future  | e F           | lese | arch | 1.  |     |     |      | •    |               |     |     |    |   |   |       |       |   | • |   |       | . 108 | ,<br>, |

|   | DIE | BLIOG   | 'D            | ۸D   | uv   |     |     |     |      |      |               |     |     |    |   |   |       |       |   |   |   |       | 110   | •      |

|   | DIL | DLIOG   | ΓIÙ.          | АΓ   | TT T |     |     |     |      |      |               |     |     |    |   |   |       |       |   |   |   |       | TTC   | ,      |

# List of Tables

| 2.1 | Some design issues in media storage and retrieval techniques         | 28 |

|-----|----------------------------------------------------------------------|----|

| 3.1 | Peak throughput of three network applications for leading general-   |    |

|     | purpose processors with different internal bus bandwidth. The ex-    |    |

|     | ternal (e.g., PCI) bus is assumed to be 64 bits wide and operates at |    |

|     | 133 MHz with a 1066 MBytes/Sec bandwidth                             | 47 |

| 4.1 | Comparison of streaming media server performance with respect to     |    |

|     | selected metrics                                                     | 66 |

| 4.2 | Comparison of Apache and IIS web servers for an average file size of |    |

|     | 10 KB                                                                | 78 |

| 4.3 | Comparison of Apache and IIS web server performance                  | 79 |

| 4.4 | Summary of IP forwarding performance.                                | 89 |

# List of Figures

| 2.1 | An example of using array padding to reduce conflict misses             | 11 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | An array restructuring example to store the sequentially accessed data  |    |

|     | in contiguous memory locations                                          | 12 |

| 2.3 | An example of loop nest modification with array restructuring to        |    |

|     | minimize strides.                                                       | 13 |

| 2.4 | Proxy server setup consisting of an origin server, wide-area network,   |    |

|     | and edge of a network                                                   | 17 |

| 3.1 | Architecture of a typical server built on a general-purpose platform    |    |

|     | with four data transfer paths                                           | 34 |

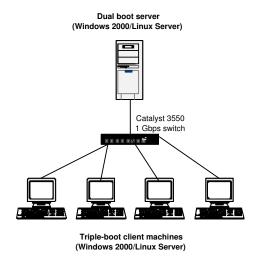

| 4.1 | Experimental testbed consisting of a dual boot server and triple-boot   |    |

|     | client machines connected through Cisco catalyst 3550 switch            | 50 |

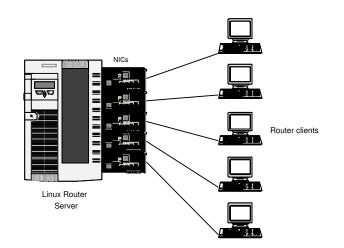

| 4.2 | IP forwarding testbed consisting of router machine and routing clients. | 50 |

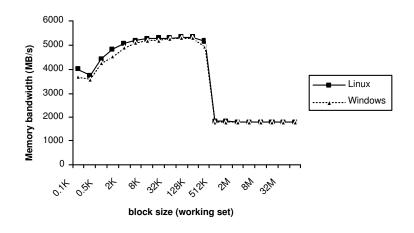

| 4.3 | Extended copy transfer characterization (stride = 1). $\ldots$          | 53 |

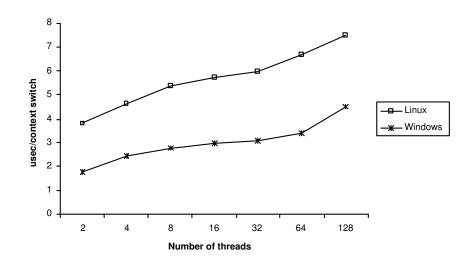

| 4.4 | Context switching overhead on Linux and Windows                         | 55 |

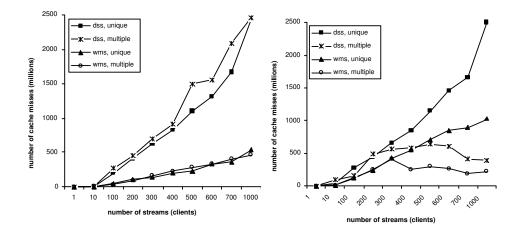

| 4.5  | Server L1 cache misses: (a) at 56 Kbps encoding (b) at 300 Kbps      |    |

|------|----------------------------------------------------------------------|----|

|      | encoding                                                             | 61 |

| 4.6  | Server L2 cache misses: (a) at 56 Kbps encoding (b) at 300 Kbps      |    |

|      | encoding                                                             | 61 |

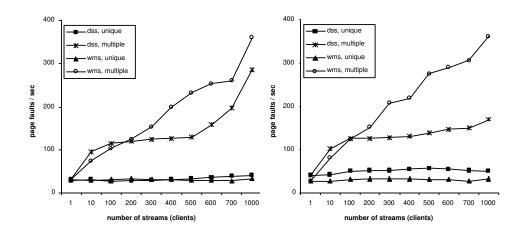

| 4.7  | Server page fault rates (a) at 56 Kbps encoding (b) at 300 Kbps      |    |

|      | encoding                                                             | 63 |

| 4.8  | Server Throughput (a) at 56 Kbps encoding (b) at 300 Kbps encoding.  | 64 |

| 4.9  | Server CPU utilization (a) at 56 Kbps encoding (b) at 300 Kbps       |    |

|      | encoding                                                             | 65 |

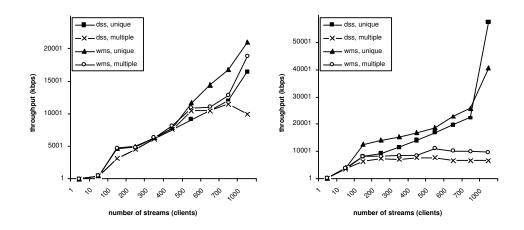

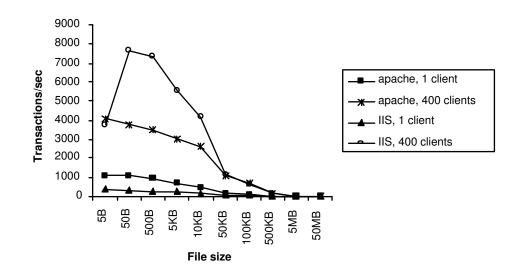

| 4.10 | Variation of server transactions with file size                      | 72 |

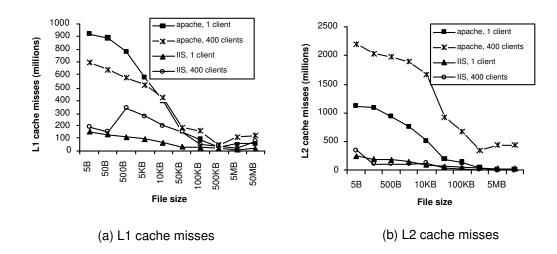

| 4.11 | Variation of server cache misses with file size                      | 73 |

| 4.12 | Variation of server page fault rate with file size                   | 75 |

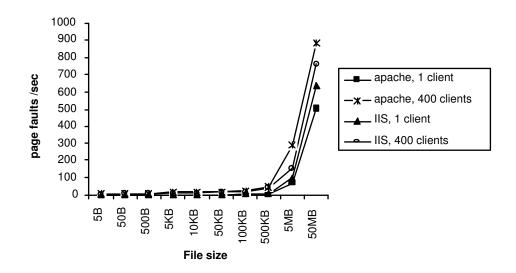

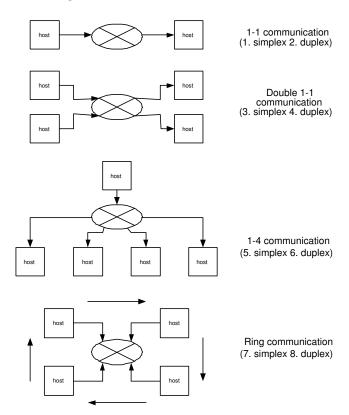

| 4.13 | Variation of server (a) throughput, (b) latency and (c) CPU utiliza- |    |

|      | tion with file size                                                  | 76 |

| 4.14 | Routing configurations showing simplex and duplex modes              | 81 |

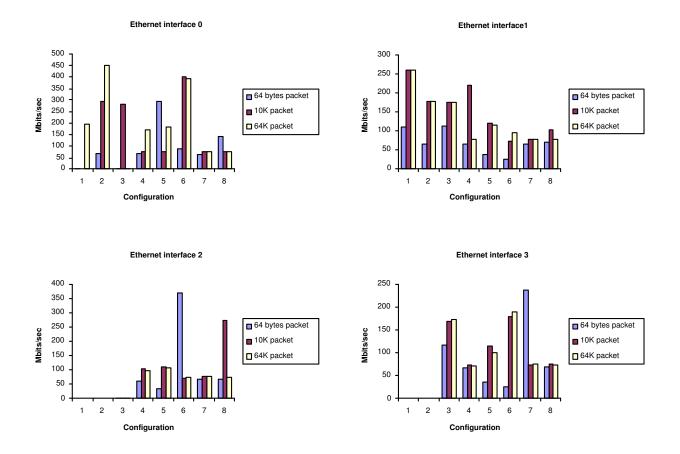

| 4.15 | Router NICs throughput                                               | 85 |

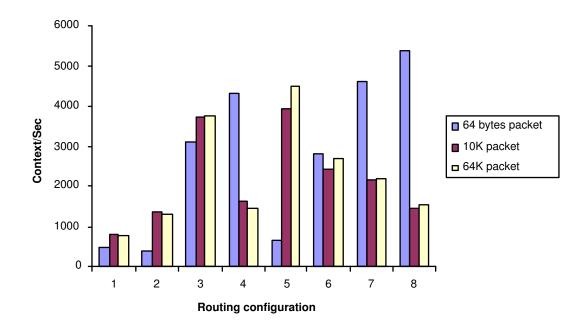

| 4.16 | Variation of context switching rate with routing configuration       | 86 |

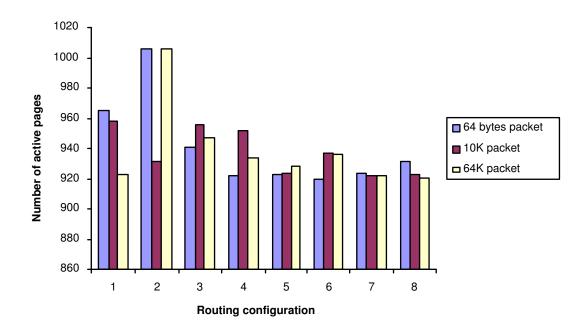

| 4.17 | Variation of number of active pages with routing configuration       | 87 |

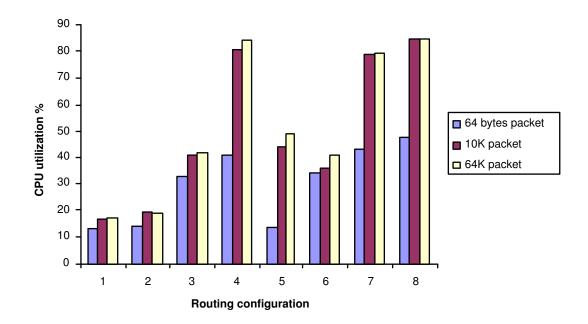

| 4.18 | Variation of CPU Utilization with routing configuration.             | 88 |

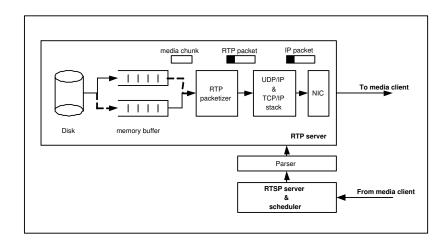

| 5.1  | Architecture of a double buffer RTP server                           | 93 |

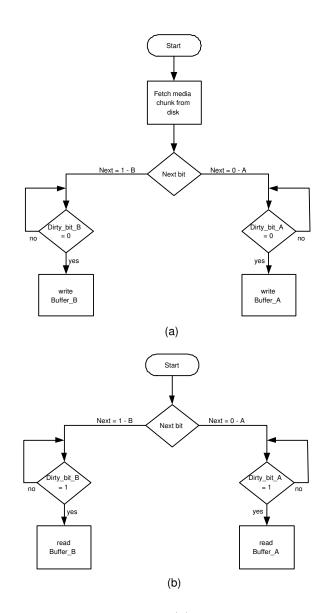

| 5.2 | Illustration of double buffering (a) Writing to the double buffer (b) Read-                                           |

|-----|-----------------------------------------------------------------------------------------------------------------------|

|     | ing from the double buffer                                                                                            |

| 5.3 | Screen shot of DB-RTP server packets captured during streaming                                                        |

|     | session                                                                                                               |

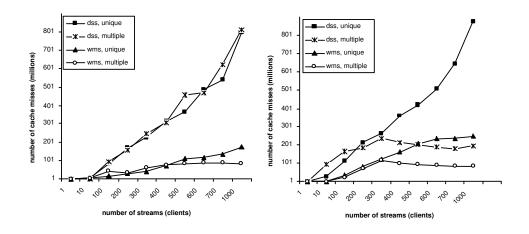

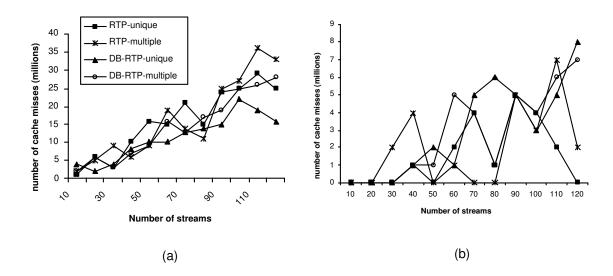

| 5.4 | Variation of server cache misses with number of clients (a) L1 cache                                                  |

|     | misses (b) L2 cache misses. $\ldots$ |

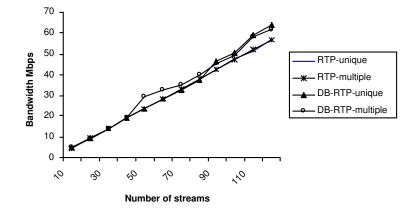

| 5.5 | Server aggregate throughput (in terms of total bytes transferred per                                                  |

|     | second)                                                                                                               |

| 5.6 | Server CPU utilization                                                                                                |

| 5.7 | Streaming client jitter                                                                                               |

#### THESIS ABSTRACT

Name:Garba Ya'u IsaTitle:Memory Performance Evaluation of High Throughput ServersMajor Field:Computer EngineeringDate of Degree:June 2003

High throughput of network infrastructure servers largely depends on their memory performance. While processor speed has been doubling roughly every eighteen months, memory access latencies reduce at a rate of about 10% per year. Bottleneck in server performance has been shifting from processor to cache, main memory and virtual memory performance. In this thesis, we analytically model memory access of transactions in three key high throughput servers: streaming media servers, web servers and software routers. We obtain optimistic peak throughputs of these servers for state-of-the-art general purpose processors with varying internal bus speeds. We also conduct a measurement-based performance evaluation of these high throughput servers. We identify memory subsystem as a potential performance bottleneck for streaming media servers and web servers, while context switching overhead and bus contention have greater impact on performance of software routers. To demonstrate how memory latency hiding can improve server performance, we design and implement a prototype RTP server that incorporates multithreading, and pre-fetching with buffering to hide memory (main and virtual) access latency. We evaluate the performance of our prototype against an RTP server, which does not incorporate above memory performance improvements and report that our prototype shows higher throughput with lower jitter.

### MASTER OF SCIENCE DEGREE

King Fahd University of Petroleum & Minerals, Dhahran, Saudi Arabia.

June 2003

### خلاصة الرسالة

الإســـــم : جاربا ياؤو عيسى عنوان الرسالة: تقييم كفاءة الذاكرة في الخادمات ذات الإخراج العالي التخصص: هندسة الحاسب الآلي تاريخ التخرج: يونيو 2003م

تعتمد الخادمات ذات الطاقة العالية والتي تبنى منها الشبكة بدرجة علية على كفاءة ذاكر اتها. فبينما ازدادت سرعة المعلج إلى حوالي الضعف كل ثمانية عشر شهرا ، نتضاءل تأخر الوصول إلى الذاكرة إلى 10% في كل سنة تقريبا. فالإعاقة في كفاءة الخادم قد تحول من المعالج إلى كفاءة الذاكرة الفورية (cache) ، الذاكرة الرئيسية و الذاكرة الإفتر اضية. في هذه الرسالة ، قمنا بصياغة تحليلية لوصول الذاكرة في ثلاث خادمات ذات اخراج عالى: خادمات الملتيميديا، خادمات الويب و موجهات (routers) ، الذاكرة الرئيسية و الذاكرة الإفتر اضية. في هذه الرسالة ، قمنا الخادمات الويب و موجهات (routers) البرامج. لقد حصلنا على الطاقة القصوى المتقالة لهذه الخادمات لأحدث المعالجات ذات الأغر اض المتعددة مع سرعات متغير للناقل الداخلي (internal أن نظام الذاكرة يمثل عائق كامن لكفاءة خادمات الملتيميديا وخادمات الولية . ولقد تعلمنا أن نظام الذاكرة يمثل عائق كامن لكفاءة خادمات الملتيميديا وخادمات الويب ، بينما تمثل تحول إلى نظام الذاكرة يمثل عائق كامن لكفاءة خادمات الملتيميديا وخادمات الويب ، بينما تمثل تحول السيلق (context switching) ومقاومة الناقل العائق الأكبر لموجهات البرامج. حتى نبين مدى تثرير إخفاء الوصول إلى الذاكرة على تحسين أداء الخادم ، تم تصميم وتطبيق نموذج خادم أر تي بي (RTP) والذي يتضمن على تعدد الخيوط (multithreading) ، وطريقة الاستجلاب بي (RTP) والذي يتضمن على تعدد الخيوط (multithreading) ، وطريقة الاستجلاب بي التمهيدي مع استخدام الذاكرة المسانده لإخفاء تأخر الوصول إلى الذاكرة (لرئيسية والإفتر اضية). النمونجنا أداء نمونجنا مع خادم آر تي بي والذي لم يظهر عليه أي تحسين في أداء الذاكرة و ذكرنا أن نمونجنا أناء نمونجنا مع خادم آر تي بي والذي لم يظهر عليه أي تحسين في أداء الذاكرة و ذكر المريسية والإفتر اضية).

## Chapter 1

## Introduction

High throughput of network infrastructure servers largely depends on their memory performance. While processor speed has been doubling roughly every eighteen months, memory access latencies reduce at a rate of about 10% per year. Bottleneck in server performance has shifted from processor to memory hierarchy, which includes cache, main memory and virtual memory performance.

This thesis is an outcome of our efforts to study the impact of memory subsystem performance on high throughput servers. It reports the results of our static analysis of memory access patterns and throughput of selected network applications. It also presents an in-depth measurement-based study of memory performance of three representative high throughput servers. In addition, a customized RTP server was implemented to investigate the benefits of memory latency hiding.

In this introductory chapter, we present a general background of this thesis.

We discuss memory subsystem issues related to the performance of high throughput servers. This discussion motivates the primary question that this thesis investigates: how on-chip cache, main memory, and disk can become significant performance bottleneck for high throughput servers in the context of network infrastructure applications.

## 1.1 High Throughput Servers

Growing use of the Internet requires high performance servers for such applications as World Wide Web (WWW) and real-time multimedia applications. Web servers, streaming servers, and software routers (henceforth, collectively termed as high throughput servers) are essentially high performance transaction processing engines that normally serve a large number of clients. The continuous growth of the Internet makes high throughput demands on these servers even more stringent; hence the performance of these servers must meet up with the demands in today's Internet applications and large number of clients.

### 1.1.1 Server Performance Issues

Due to growing interest in the development of novel technologies targeted at commerce and other critical applications, the performance of high throughput servers has become a key aspect in the design of information infrastructure. The objective is to fulfill the growing requirement of offering access to an ever increasing volume of requests for information consisting of text, image, audio, and video from a large number of clients distributed across the Internet. Similarly, since its introduction in early 1990s, the concept of streaming media has experienced a dramatic growth and transformation from a novel technology into one of the mainstream manners in which people experience the Internet today. Indeed, such growth would not be possible without adequate progress in the development of various core technologies utilized by streaming media software and hardware.

Streaming servers need to retrieve media components in a synchronous fashion. These servers deliver live or on-demand audio or video content to potentially thousands of clients distributed across the Internet. Because of the stringent timing and quality-of-service requirements, high-bandwidth demands, and the CPU and memory intensive characteristics of these applications, the performance of the server hardware is critical for efficient performance and delivery of high quality multimedia contents.

Proxy server usage is growing and caching proxies have gained widespread deployment on the Internet. Frequent requests for a small number of popular objects have made caching highly successful in reducing server load, network congestion, and client perceived latency [1]. While most of the caching research to date has focused on caching of textual and image objects, streaming proxies are becoming increasingly popular. Caching streaming media objects with proxy servers poses many new performance challenges [2]. The key challenge in designing such proxy servers is that they need to deal with heterogeneity in data characteristics as well as heterogeneity in the service requirements of applications.

### 1.1.2 Memory Hierarchy

There has been tremendous progress in microprocessor technology that leads to high speed CPUs. Also, advances in memory and magnetic disk technology have significantly improved memory and magnetic disk densities. However, memory and disk access and cycle times have lagged far behind improvements in their densities. Density of semiconductor DRAM and magnetic disks increase by approximately 50 -60% per year, quadrupling in three years, but cycle time has improved very slowly, decreasing by about one-third in 10 years [3].

To alleviate the problem of widening performance gap between processor and main memory, computer architecture incorporates a hierarchical memory system in which data caches are widely used for hiding memory latency. Memory hierarchy is based on the principle of locality of reference – temporal and spatial. Temporal locality states that recently accessed data are likely to be accessed in the near future while spatial locality means that data whose addresses are near one another tend to be referenced close together in time [3]. Caches go a long way in improving performance for applications with small working data sets and large amounts of spatial and temporal locality. Often a small cache can provide enough storage to hold most of the useful data required by the program at any time during its execution. If an application code is not tuned to exploit these locality characteristics, it may fail to achieve desired performance improvements.

### **1.2** Problem Statement

With current technology trends where processor-memory speed imbalance remains wide, tuning a program's memory performance has become increasingly important. Many research efforts have focused on improving the cache performance of scientific programs that use arrays as their primary data structure. Unfortunately, these techniques do not directly apply to high throughput servers. It is obvious that memory and disk overheads can inhibit the performance of any busy high throughput server. In this work, we are interested in the memory performance evaluation of high throughput servers to determine the specific conditions under which on-chip cache or memory becomes a major performance bottleneck for the server. Identifying these conditions is essential and will serve as a bed-rock for server design. This initial step will result in alleviating memory bottleneck and lead to improvement in overall performance. An efficient high throughput server must possess the following characteristics:

- Delivery of high throughput;

- Serve client transaction with minimal latency; and

• Responds to a large number of clients.

Memory performance issue in high throughput servers is a difficult problem for many reasons such as large amounts of data flowing through the CPU and memory system, mostly decreasing overall cache hit ratios and leading to a lot of memory copying. Writing code to optimize memory usage is also a complex task because of the nature of the data handled by these servers, which is difficult to tune for effective cache performance, since such data is hardly reusable and often the working set is large.

## **1.3** Contributions of this Work

This thesis addresses the memory performance problem that inhibits the performance of high throughput servers. The following are the major contributions of this thesis:

- Cache overhead analysis of various types of high throughput servers by static analysis and measurement-based experiments.

- Memory latency and bandwidth analysis and their impact on server throughput.

- Measurement-based performance evaluation of three representative network applications, namely web servers, streaming media servers, and software routers

involving Internet Protocol (IP) forwarding on general purpose computing platform.

• Design, implementation, and evaluation of a prototype streaming server, named Double Buffer RTP (DB-RTP) server.

These contributions are important for the state-of-the-art servers. For instance, understanding the role of memory performance on high throughput will give insight to a better design consideration. Addressing misconception of cache overheads for high data rate applications on general-purpose computing platform is also an essential design issue that must be addressed. Latency hiding is a viable work-around on the memory latency problem that can boost performance of applications.

### 1.4 Thesis Overview

The rest of this thesis is organized as follows. Chapter 2 provides background of high throughput servers, their performance tuning needs, evaluation methodologies, and related work. In Chapter 3, we analyze memory access pattern of network applications and calculate performance bounds based on cache and memory models. Chapter 4 reports our measurement-based memory performance study of key high throughput servers: streaming media servers, web servers, and software router for IP forwarding on general purpose computing hardware. In Chapter 5, we outline the design of our prototype streaming server that addresses some memory performance issues. We also report our performance evaluation of the prototype RTP server that incorporates latency hiding. We finally draw conclusions about this research effort and outline the future direction of this work in Chapter 6.

## Chapter 2

## **Background and Related Work**

## 2.1 Introduction

Performance tuning of servers, especially those that are required to deliver high throughput is essential to meet up the demand of increasing number of clients requiring fast and efficient service. Servers that cannot deliver clients' request with acceptable quality of service (QoS) are likely to incur business lost.

In this chapter, we discuss background issues related with high throughput servers, their performance tuning and some design considerations to boost performance, and review related work in the literature focusing on high throughput servers and memory performance improvement techniques.

## 2.2 Server Performance Tuning

High throughput servers are often based on general-purpose computing platforms. Performance tuning is one of the basic design and deployment activities for these servers. In this section, we present the server performance tuning issues with respect to memory performance, latency hiding, multithreading, multiprocessing and clustering, and special architectures.

### 2.2.1 Memory Performance Tuning

Code transformation has been used intensively to improve memory performance [3]. Compiler controlled memory performance optimizations rely on source code analysis to identify target code blocks that can be transformed to improve data reuse. The objective of this process is to reduce the cache miss rate by improving data locality. We briefly review some popular techniques in this regard.

#### Array Padding

Since cache line sizes are often equal to a power-of-two value, array dimensions that are also a power-of-two cause unnecessary conflicts to occupy identical cache lines. Although a set-associative architecture reduces the contention due to multiple sets, the severity of the problem remains significant for larger applications due to a large number of memory accesses to an equally large number of arrays. A commonly used technique to solve this problem is to pad the arrays to increase their dimensions by one [4]. Figure 2.1 shows an example of array padding in the declaration of an array, while the rest of the application code remains unchanged.

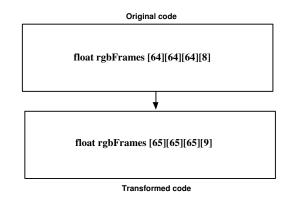

Figure 2.1: An example of using array padding to reduce conflict misses.

#### Array Restructuring

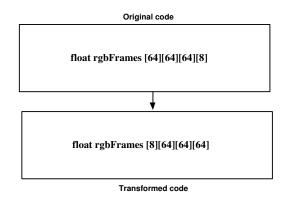

Minimization of strides of array references improves cache utilization. Unfortunately, there is no particular method of minimizing strides that can be applied in general to any given code. Array dimensions could be restructured so that the array elements that are used one after the other are stored in contiguous memory locations. Figure 2.2 shows the array declarations with their dimensions modified from the original code. The rest of the code remains unchanged.

Figure 2.2: An array restructuring example to store the sequentially accessed data in contiguous memory locations.

#### Loop Nest Transformations

Loop nest transformation is another technique that can be used for stride minimization. With a nested loop, it is best to design the loop nest in such a way that subsequent memory access hit in contiguous locations or with small strides. Figure 2.3 presents an example of an original as well as modified code segment with loop nest transformations and array restructuring to minimize strides. In order to make such a transformation, the loop body needs to be analyzed to ensure that array accesses are independent of various loop indices to allow transforming the nest without changing the end result.

Reducing the overall memory consumption by an application decreases the overall cache misses. Blocking is another technique, which is often used to improve temporal locality. In blocking, instead of operating on entire rows or columns of an array, blocked algorithms operate on submatrices or blocks with a goal of maximizing

Figure 2.3: An example of loop nest modification with array restructuring to minimize strides.

accesses to the data loaded into cache before the data is replaced [3].

### 2.2.2 Latency Hiding and Multithreading

As memory access speed remains a technology issue that is unlikely to be resolved in the near future, several techniques are used to circumvent the latency constraints. One key technique is hiding memory access latency by implementing parallelism. Novel architectures and enhanced compilers could be used where a processor can utilize the parallelism information to execute a large number of memory operations concurrently. For example, in multithreaded applications, when one thread is blocked due to memory latency, (e.g., a cache miss) or synchronization delay, the hardware switches to issuing instructions from another thread within a couple of clock cycles [5].

Some explicitly parallel architectures that are capable of providing memory latency hiding are [5]:

- EPIC (IA-64) [6]: It exposes parallelism information to the hardware using very long word instructions (VLIW).

- VIRAM [7]: Expresses parallelism to hardware in the form of vector operations.

- Impulse [8]: Allows software to describe regular memory access patterns directly to the memory controller.

### 2.2.3 Multiprocessing and Clustering

Multiprocessing and clustering have been used in several applications to boost server performance. In fact, major web servers work in clusters or involve multiprocessor architectures. An example of a cluster implementation to boost performance is the Panama cluster router [9]. It includes a cluster of PCs connected by a high speed system area network. Panama has a decoupled system architecture that separates packet forwarding and packet computation paths. It derives performance improvement from parallelization of these tasks on the cluster.

### 2.2.4 Specialized Architectures

Another trend in server performance tuning is to employ special-purpose architectures that are specifically designed for a particular application. A typical example is a network processor. A network processor is a special-purpose programmable hardware specifically designed for network systems and applications [10]. Other special purpose architectures include ASICs (application specific integrated circuits) and data flow architectures. All specialized architectures have some common features that help them deliver high performance for their applications. These features include: flexibility through programmability, optimized architecture for specific target applications, and scalability with parallelism and pipelining.

## 2.3 Examples of High Throughput Servers

Due to a large number of users on the Internet, content distribution servers on the Internet are subjected to high traffic throughput and acceptable QoS demands. Some popular network core and edge applications on the internet today are: web, proxy, streaming servers, and routers. In this section, we review the design and performance issues relevant to these high throughput servers.

### 2.3.1 Web Servers

The purpose of a web server is to provide documents to WWW clients when they request for them. A web server operates in the following way. The server listens on a designated port (usually port 80) for a request from a WWW client to establish a TCP connection. Once a TCP connection is opened and the client has made its request, the server must respond to that request. The response includes a status code to inform the client if the request has succeeded or not. If the request is successful, a document is usually returned with the response. If the request is not successful, a reason for the failure is returned to the client.

### 2.3.2 Streaming Servers

An important issue in multimedia information systems, particularly for serving video and audio contents, is QoS guarantee. Streaming media servers better address this issue than web servers. To offer quality streaming services, servers are required to process and transmit data under timing constraints. A streaming media server typically consists of three subsystems, namely, a communicator (e.g., transport protocols), an operating system, and a storage system [11]. The operating system manages the essential resources, such as the CPU, main memory, storage, and all input and output devices. Since resources are limited, the server can only serve a limited number of clients with requested QoS. Therefore, resource management is required to properly accommodate timing requirements.

### 2.3.3 Proxy Servers

A WWW proxy is an application program that accepts requests from a set of clients, forwards these requests to the appropriate servers (if required), and sends the requested data back to the clients. While receiving and serving requests from the clients, the proxy functions as a server. On the other hand, while forwarding requests to the origin servers, the proxy functions as a client. The proxies store frequently requested objects close to the clients in the hope of satisfying future client requests without contacting the origin servers. By keeping local copies of objects requested by clients, and using them to satisfy future requests for the same objects, caching proxies can reduce the amount of traffic flowing between clients and the origin servers. Proxy servers at the edges of networks are usually subjected to high transaction loads. Figure 2.4 depicts a typical proxy server setup.

Figure 2.4: Proxy server setup consisting of an origin server, wide-area network, and edge of a network.

### 2.3.4 Software Routers and IP forwarding

Routers are network devices used at edges as well as core, responsible for routing and forwarding of packets. While routing is the process of building a routing table using one or more routing algorithms, forwarding is the process of moving a packet from an input port to an output port based on the destination of the packet. Forwarding is achieved in consultation with the routing table.

Decreasing cost of general-purpose computing hardware and their increasing performance has begun to attract researchers to consider the deployment of these general-purpose hardware for IP routing and forwarding purposes. IP packet forwarding is described in RFC 1812 [12]. The following steps are involved in forwarding an IP packet:

- Verify the header checksum. If cannot verify correctness, drop the packet without any further action;

- Check for IP options;

- Look up the destination address in the forwarding table and decide which output port packet should go;

- If no route is found, return ICMP Destination Unreachable;

- If the router itself (typically its control processor) is the packet's final destination, deliver it;

- Verify that the packet's time-to-live (TTL) is > 0. If check fails, return a (possibly rate-limited) ICMP error message ("Time exceeded");

- Decrement TTL;

- Update the header checksum (if done in an error-preserving way, the initial verification can be skipped);

- Verify whether the MTU of the outgoing interface is large enough; if not, fragment; and

- Send the packet to the appropriate output interface as determined by the forwarding lookup.

Four most important performance issues related to router performance are: (i) use of interrupts, (ii) bus bandwidth, (iii) speed of the CPU, and (iv) bandwidth of the memory. Time taken to process interrupts can be quite significant for high performance routing. Any amount of time taken between hardware generating an interrupt and reading relevant data is a direct contributor to latency within the router. Bus bandwidth in the router host is very important. The machine bus is the common communication channel that nearly all hardware components use to communicate. When attempting to route between a number of separate devices, it is possible for the bus to become a performance bottleneck due to contention. The CPU can also be a performance bottleneck especially when there is a lot of processing due to firewall or NAT (network address translation) rules [13].

### 2.4 Evaluation Methodologies

System performance evaluation falls under one of the following methodologies: static analysis, simulation or measurement. In static analysis, mathematical equations representing a model of the system can provide insight on performance, especially bounds (lower or upper limits on performance). In static analysis, mostly accuracy is compromised to some extent for simplicity. Trace driven simulation technique is well-known for designing and analyzing processor caches. Instrumented applications are executed to obtain a trace of all memory accesses (load and store addresses with or without size of data transfer) in a benchmark program. This trace is consumed by a simulator that can predict the cache performance of a new architecture whose design parameters, such as cache line size, degree of associativity, capacity, etc., can be evaluated under such workload. Unlike the other two methods, measurement requires an existing system or a prototype. Measurement based evaluation provides the most realistic assessment of system performance and behavior, though it takes more time and is likely to be more expensive. Processor on-chip counters are frequently used to capture low level measurements of metrics like cache misses, instruction cycles, etc.

## 2.5 Related Work

In this section, we provide an overview of related work in the literature. We discuss research efforts towards improving memory performance using several techniques such as improving cache miss rate and use of memory compression. We also review work on performance evaluation of high throughput servers and video server design issues. We finally discuss work on routing and IP forwarding on general-purpose computing platform.

### 2.5.1 Improving Memory Performance

Improving cache miss rate has significant impact on memory system performance since high miss penalty will be minimized. Another approach for improving memory speed is by increasing the bandwidth, which will effectively improve memory access latency. Compressing memory pages minimize the tendency of swapping such pages to disk, hence minimizing slow disk access by keeping the compressed page in memory.

#### Performance of Cache and TLB

The most important performance parameters of a memory hierarchy are cache miss latency, TLB (Translation Lookaside Buffer) miss latency, and effective data path parallelism [14]. The substantial research efforts on improving the performance of

cache, memory, and TLB shows the extent of their importance. So many techniques have been proposed in the literature for improving cache performance by either reducing miss rates or miss penalty. Techniques for minimizing cache miss rate include use of larger cache block size and large cache capacity, higher associativity, use of victim caches, implementing pseudo-associative caches, hardware prefetching of instructions and data, compiler-controlled prefetching and compiler optimizations [3]. Cache miss penalty could also be reduced by: (1) giving priority to read misses over write misses; (2) use of early restart and critical word first; (3) use of nonblocking caches to reduce stalls on cache misses; and (4) use of second and third level caches [3]. Not surprisingly, most of the research efforts on improving cache performance are on numerical applications [15, 16, 17, 18]. Few cases have been reported on the study and optimizing cache performance for other applications like database systems [19, 20, 21, 22, 23]. Cache misses could be represented analytically, providing a general framework to guide code optimizations for improving cache performance. Cache miss equations have been used to determine array padding and offset amounts that minimize cache misses [24]. High throughput servers will benefit from some of these techniques like nonblocking caches that will reduce stalls on cache misses and use of larger cache block size since working set for the servers are mostly large.

#### Improving Main Memory Performance

Since reducing latency of memory has been a slow process, it is generally easier to improve memory bandwidth with novel organizations than it is to reduce memory access latency. Several techniques have also been reported in the literature for improving memory bandwidth. These techniques include (1) wider main memory, (2) simple interleaved memory to take advantage of the potential parallelism of having many DRAMs in a memory system, (3) independent memory banks that will allow multiple independent accesses, (4) avoiding memory bank conflicts, and (5) DRAM-specific interleaving [3]. High throughput servers that require transfer of large block of data will benefit from a wider main memory, effectively minimizing memory access latency. The parallelism inherent in memory interleaving is also good for these servers.

#### System Software Modifications

Several memory performance tuning approaches are based on modifying operating system, compiler, or even application source code. Recent work on memory performance tuning has proposed compressing memory pages in preference to swapping them out to disk [25, 26, 27, 28, 29]. The goal of memory compression is to hide the disk latencies by storing swapped out page frames in a compressed form, while residing in physical memory. On a subsequent page fault, the page can be quickly decompressed and supplied to the application program. Roy et al [30] implemented

a compressed memory on a Linux operating system. Their implementation is in the form of a loadable device driver, which can simply be unloaded for those applications that do not benefit from memory compression. The implementation shows speedups ranging from 5% to 250% on SPEC 2000 benchmarks and computational kernel applications. Researchers working on the Impulse Project [31, 32] introduced an optional level of address translation at the memory controller. This feature exploits "unused" physical addresses that can be translated to "real" physical addresses at the memory controller. Using Impulse requires modifications to applications (or compilers) and operating systems, but requires no hardware modifications to processors, caches, or buses. Impulse can reportedly speed-up a range of applications from 20% to over a factor of 5. Memory compression may not be a suitable alternative for high throughput servers since reusability of data is minimal. Keeping a compressed data in memory that is likely not be used again is not an advantage.

#### 2.5.2 Performance Evaluation of High Throughput Servers

We present performance evaluation methodologies and performance analysis of high throughput servers. We outline some video server design issues. We similarly review research efforts on software routing and IP forwarding on general-purpose computing platform.

#### **Streaming Media Servers**

Performance of a streaming server is a key factor contributing to the quality of the multimedia content for the end-users. Shenoy et al [33] highlighted some fundamental issues arising in multimedia server design. Technical challenges in design such as storage and retrieval of multiresolution data, scalability and management were presented. Sohn et al [34] evaluated the performance of a small-scale Video on Demand (VOD) server. They conducted a measurement-based study in which they outlined the predictability of the real-time scheduler and the performance of the VOD server. Results of the performance measurements showed that the network protocol processing is a source of non-predictability. They found that high performance processor should be used to process the network protocol. However, the performance of the storage system was not a problem to the VOD service.

A significant amount of work is reported in the literature on the disk storage performance for streaming media servers. Due to large volumes of video and other multimedia content, storage and retrieval techniques play an important role in the performance of the server. A storage hierarchy to design a low-cost cache for a movie on demand (MOD) server was proposed in [35]. The hierarchy consists of a disk, which stores the popular movies, and a small amount of RAM buffers that store only part of the movies. Due to low cost of disks, the cost of a MOD server based on the proposed architecture is substantially lower than one in which the entire movie is loaded into RAM. Another multimedia architecture and data retrieval model for supporting simultaneously multiple clients requesting files of different playback rates is presented in [36]. The performance of the architecture was investigated using a circular SCAN disk scheduling policy in terms of the maximum number of concurrent video streams it can support.

Some studies of multimedia servers pay attention to I/O subsystems due to high throughput demand of the servers. In fact, streaming media servers are often I/O bound. A study focused on the design of an I/O subsystem for a continuous media server is reported by Weeks et al [37]. They proposed several improved architectures based on an existing device: Intel i960RP I/O processor, and evaluated their performance. They reported that utilization of the I/O processor solved the main memory bottleneck problem, but created a new bottleneck in i960RP memory. I/O performance in multimedia servers has also been investigated using simulation [38]. Various I/O issues in multimedia systems have been discussed in [39], focusing on disk scheduling, SCSI bus contention and effect of buffer space on the performance of real-time requests and aperiodic requests.

Rixner [40] proposed the Imagine architecture for streaming media processor, which delivers a peak performance of 20 billion floating-point operations per second. Imagine efficiently supports 48 arithmetic units with a three-tiered data bandwidth hierarchy. At the base of this hierarchy, streaming media system employs memory access scheduling to maximize the sustained bandwidth of external DRAM. At the center of the hierarchy, global stream register file enables streams of data to be recirculated directly from one computation kernel to the next without returning these data to memory. Also, local distributed register files that directly feed the arithmetic units enable temporary data to be stored locally so that it does not consume costly global register bandwidth. The bandwidth hierarchy enables Imagine to achieve up to 96% of the performance of a stream processor with infinite memory bandwidth from memory and the global register file.

#### **Design of Video Servers**

Several designs and architectures of video servers have been reported as improving one or even some aspect of performance of the servers. Bulk of the work however addresses the issue of storage and disk performance. Issues in multimedia server design are presented in [33].

The fundamental design issue is that of addressing quality of service constraints like delay, jitter and packet loss while also enhancing the capability of the server to handle large number of concurrent streams of video. Table 2.1 outlines some techniques in the design of video servers.

|                 | Techniques           | References           |  |

|-----------------|----------------------|----------------------|--|

| Media storage   | Data striping        | [41, 11]             |  |

|                 | Hierarchical storage | [11]                 |  |

|                 | Fault tolerance      | [42, 43, 44, 45, 46] |  |

| Media retrieval | Buffering            | [47, 48]             |  |

|                 | Caching              | [49, 47]             |  |

|                 | Batching             | [50, 51]             |  |

Table 2.1: Some design issues in media storage and retrieval techniques.

#### Web and Proxy Servers

Web servers are key part of the Internet infrastructure today since web traffic accounts for substantial proportion of the traffic on the Internet. There has been tremendous amount of work on web servers ranging from performance studies to workload characterization [52] and even security issues [53, 54]. But just like the case of streaming media servers, there is no significant work on the performance of cache and memory subsystem. Iyengar et al report [55] performance study focused on improving the performance of the web server in the situation where the CPU becomes the limiting resource. In [56] a new web server mechanism was reported. JAWS was designed as an object-oriented web server that was explicitly meant to alleviate the performance bottlenecks identified in existing web servers. The performance optimizations used in JAWS included adaptive pre-spawned threading, intelligent caching, and prioritized request processing. Performance results were presented showing the scalability and efficiency of the proposed design. This is an attempt to improve the performance of the web server itself and not the underlaying hardware.

Comparative performance characteristics are often studied using web server benchmarking tools. A measurement based performance study of Apache and Microsoft Internet Information server is reported in [57]. Their study focused on comparative performance on same hardware, but no attention was paid on the impact of the underlaying hardware. Trecordi and Verger [58] studied the main factors affecting the performance and scalability of web servers. They take into account the impacts of the server software architecture, operating system and the underlaying server hardware. They reported numerical results that reveal that the performance and scalability of WWW servers heavily depend on a lot of parameters that should be properly tuned. Although this study discussed cache and virtual memory system, no measurement on any metric related to the cache and virtual memory was reported.

#### 2.5.3 Software Routing and IP Forwarding